239:

295:(EPIC). Intel's goal was to leverage the expertise HP had developed in their early VLIW work along with their own to develop a volume product line targeted at the aforementioned high-end systems that could be sold to all original equipment manufacturers (OEMs), while HP wished to be able to purchase off-the-shelf processors built using Intel's volume manufacturing and contemporary process technology that were better than their PA-RISC processors.

713:

RISC processors of the time, and no-ops due to wasted slots further decrease the density of code. Additional instructions for speculative loads and hints for branches and cache are impractical to generate optimally, because a compiler cannot predict the contents of the different cache levels on a system running multiple processes and taking interrupts.

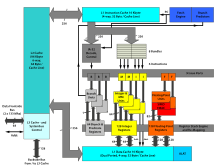

741:. The Itanium 2 bus was initially called the McKinley bus, but is now usually referred to as the Itanium bus. The speed of the bus has increased steadily with new processor releases. The bus transfers 2×128 bits per clock cycle, so the 200 MHz McKinley bus transferred 6.4 GB/s, and the 533 MHz Montecito bus transfers 17.056 GB/s

519:. It uses variable-sized register windowing for parameter passing. The same mechanism is also used to permit parallel execution of loops. Speculation, prediction, predication, and renaming are under control of the compiler: each instruction word includes extra bits for this. This approach is the distinguishing characteristic of the architecture.

431:

The very next day on 5th

October 1999, AMD announced their plans to extend Intel's x86 instruction set to include a fully downward compatible 64-bit mode, additionally revealing AMD's newly coming x86 64-bit architecture, which the company had already worked on, to be incorporated into AMD's upcoming

307:

Intel's product marketing and industry engagement efforts were substantial and achieved design wins with the majority of enterprise server OEMs, including those based on RISC processors at the time. Industry analysts predicted that IA-64 would dominate in servers, workstations, and high-end desktops,

622:

indicating which type of instruction is in each slot. Those types are M-unit (memory instructions), I-unit (integer ALU, non-ALU integer, or long immediate extended instructions), F-unit (floating-point instructions), or B-unit (branch or long branch extended instructions). The template also encodes

287:

During this time, HP had begun to believe that it was no longer cost-effective for individual enterprise systems companies such as itself to develop proprietary microprocessors. Intel had also been researching several architectural options for going beyond the x86 ISA to address high-end enterprise

712:

In practice, the processor may often be underutilized, with not all slots filled with useful instructions due to e.g. data dependencies or limitations in the available bundle templates. The densest possible code requires 42.6 bits per instruction, compared to 32 bits per instruction on traditional

645:

The IA-64 assembly language and instruction format was deliberately designed to be written mainly by compilers, not by humans. Instructions must be grouped into bundles of three, ensuring that the three instructions match an allowed template. Instructions must issue stops between certain types of

327:

By 1997, it was apparent that the IA-64 architecture and the compiler were much more difficult to implement than originally thought, and the delivery of

Itanium began slipping. Since Itanium was the first ever EPIC processor, the development effort encountered more unanticipated problems than the

278:

in each clock cycle. Typical VLIW implementations rely heavily on sophisticated compilers to determine at compile time which instructions can be executed at the same time and the proper scheduling of these instructions for execution and also to help predict the direction of branch operations. The

721:

From 2002 to 2006, Itanium 2 processors shared a common cache hierarchy. They had 16 KB of Level 1 instruction cache and 16 KB of Level 1 data cache. The L2 cache was unified (both instruction and data) and is 256 KB. The Level 3 cache was also unified and varied in size from

631:, regardless of their bundling, and must be free of many types of data dependencies; this knowledge allows the processor to execute instructions in parallel without having to perform its own complicated data analysis, since that analysis was already done when the instructions were written.

552:

registers. The floating-point registers are 82 bits long to preserve precision for intermediate results. Instead of a dedicated "NaT" trap bit like the integer registers, floating-point registers have a trap value called "NaTVal" ("Not a Thing Value"), similar to (but distinct from)

279:

value of this approach is to do more useful work in fewer clock cycles and to simplify processor instruction scheduling and branch prediction hardware requirements, with a penalty in increased processor complexity, cost, and energy consumption in exchange for faster execution.

367:(the last three were canceled before reaching the market). In 1999, Intel led the formation of an open-source industry consortium to port Linux to IA-64 they named "Trillium" (and later renamed "Trillian" due to a trademark issue), which was led by Intel and included

658:

into the pipeline. When the compiler can take maximum advantage of this, the processor can execute six instructions per clock cycle. The processor has thirty functional execution units in eleven groups. Each unit can execute a particular subset of the

298:

Intel took the lead on the design and commercialization process, while HP contributed to the ISA definition, the Merced/Itanium microarchitecture, and

Itanium 2. The original goal year for delivering the first Itanium family product, Merced, was 1998.

634:

Within each slot, all but a few instructions are predicated, specifying a predicate register, the value of which (true or false) will determine whether the instruction is executed. Predicated instructions which should always execute are predicated on

803:

Cache enhancements: Montecito added a split L2 cache, which included a dedicated 1 MB L2 cache for instructions. The original 256 KB L2 cache was converted to a dedicated data cache. Montecito also included up to 12 MB of on-die L3

663:, and each unit executes at a rate of one instruction per cycle unless execution stalls waiting for data. While not all units in a group execute identical subsets of the instruction set, common instructions can be executed in multiple units.

776:

Hardware multithreading: Each processor core maintains context for two threads of execution. When one thread stalls during memory access, the other thread can execute. Intel calls this "coarse multithreading" to distinguish it from the

701:, a single floating-point instruction can perform the work of two instructions when the application requires a multiply followed by an add: this is very common in scientific processing. When it occurs, the processor can execute four

760:

architecture to permit support for legacy server applications, but performance for IA-32 code was much worse than for native code and also worse than the performance of contemporaneous x86 processors. In 2005, Intel developed the

985:

461:

In

January 2019, Intel announced that Kittson would be discontinued, with a last order date of January 2020, and a last ship date of July 2021. In November 2023, IA-64 support was removed from the

1426:

1345:

1163:"Sun Introduces Solaris Developer Kit for Intel to Speed Development of Applications On Solaris; Award-winning Sun Tools Help ISVs Easily Develop for Solaris on Intel Today"

1374:

796:: Intel added Intel Virtualization Technology (Intel VT-i), which provides hardware assists for core virtualization functions. Virtualization allows a software "

977:

259:. Both Intel and HP researchers had been exploring computer architecture options for future designs and separately began investigating a new concept known as

598:

128 special purpose (or "application") registers, which are mostly of interest to the kernel and not ordinary applications. For example, one register called

328:

team was accustomed to. In addition, the EPIC concept depended on compiler capabilities that had never been implemented before, so more research was needed.

1162:

274:) where a single instruction word contains multiple instructions encoded in one very long instruction word to facilitate the processor executing multiple

1430:

2668:

1580:

2485:

2673:

697:

Ideally, the compiler can often group instructions into sets of six that can execute at the same time. Since the floating-point units implement a

2854:

2771:

2683:

1533:

1507:

1481:

1308:

1282:

765:(IA-32 EL), a software emulator that provides better performance. With Montecito, Intel therefore eliminated hardware support for IA-32 code.

2869:

2688:

2678:

2663:

2490:

1335:

627:

which indicate that a data dependency exists between data before and after the stop. All instructions between a pair of stops constitute an

1107:

2480:

1693:

1601:

1232:

1082:

198:

architectures, which depend on the processor to manage instruction dependencies at runtime. In all

Itanium models, up to and including

2716:

1651:

292:

67:

1451:

1636:

878:

2776:

602:

points to the second stack, which is where the hardware will automatically spill registers when the register window wraps around.

1140:

843:

441:

As AMD was never invited to be a contributing party for the IA-64 architecture and any kind of licensing seemed unlikely, AMD's

399:. As a result, a working IA-64 Linux was delivered ahead of schedule and was the first OS to run on the new Itanium processors.

2859:

438:. AMD also signaled a full disclosure of the architecture's specifications and further details to be available in August 2000.

814:

1837:

1822:

1746:

1736:

1009:

453:, as opposed to Intel's approach of creating an entirely new, completely x86-incompatible 64-bit architecture with IA-64.

1741:

1661:

907:

1367:

1191:

1050:

1761:

1756:

1751:

2535:

2392:

925:

698:

291:

Intel and HP partnered in 1994 to develop the IA-64 ISA, using a variation of VLIW design concepts which Intel named

271:

252:

503:

It is a 64-bit register-rich explicitly parallel architecture. The base data word is 64 bits, byte-addressable. The

2726:

2706:

1969:

1815:

1793:

1788:

1783:

1778:

1731:

1726:

1641:

793:

2651:

1798:

1773:

1254:

955:

2864:

1964:

1933:

1904:

1686:

615:

275:

2036:

1945:

1805:

1768:

1721:

212:

187:

2833:

2007:

1957:

1921:

1570:

1170:

158:

2031:

2002:

1994:

1952:

1940:

1916:

646:

data dependencies, and stops can also only be used in limited places according to the allowed templates.

1810:

230:

In 2019, Intel announced the discontinuation of the last of the CPUs supporting the IA-64 architecture.

1909:

356:

260:

176:(HP), and was subsequently implemented by Intel in collaboration with HP. The first Itanium processor,

1309:"AMD Releases x86-64 Architectural Specification; Enables Market Driven Migration to 64-Bit Computing"

574:

64 one-bit predicate registers. These have 16 static registers and 48 windowed or rotating registers.

2874:

2786:

1679:

1312:

1286:

94:

1529:

1503:

1477:

2564:

1716:

1702:

121:

2828:

2803:

2397:

723:

683:

177:

2818:

1874:

1864:

1859:

1827:

1117:

308:

and eventually supplant both RISC and CISC architectures for all general-purpose applications.

205:

1400:

2808:

2530:

1221:

978:"Exit interview: Retiring Intel chairman Craig Barrett on the industry's unfinished business"

769:

762:

727:

531:

512:

256:

127:

62:

1612:

1071:

480:

The architecture has been renamed several times during its history. HP originally called it

2140:

945:

2410:

1530:"The Itanium processor, part 3: The Windows calling convention, how parameters are passed"

8:

2766:

2256:

1455:

200:

722:

1.5 MB to 24 MB. The 256 KB L2 cache contains sufficient logic to handle

449:

capabilities to the existing x86 architecture, while still supporting legacy 32-bit x86

2813:

2646:

2641:

2428:

2112:

2107:

2102:

2097:

2092:

867:

527:

508:

445:

architecture-extension was positioned from the beginning as an evolutionary way to add

114:

2636:

2631:

2626:

2621:

2616:

2611:

2606:

2601:

2596:

705:

per cycle. For example, the 800 MHz

Itanium had a theoretical rating of 3.2

530:, which are 64-bit plus one trap bit ("NaT", which stands for "not a thing") used for

2579:

2463:

2433:

1132:

921:

835:

772:, Intel made a number of enhancements to the basic processor architecture including:

516:

332:

321:

1646:

868:"Inventing Itanium: How HP Labs Helped Create the Next-Generation Chip Architecture"

2574:

2552:

2516:

2314:

2208:

2063:

1895:

1850:

1262:

1258:

911:

446:

396:

384:

376:

313:

2171:

2144:

1655:

1336:"Intel to Discontinue Itanium 9700 'Kittson' Processor, the Last of the Itaniums"

872:

778:

660:

535:

504:

474:

368:

264:

173:

131:

84:

35:

2711:

2375:

1017:

904:

Proceedings of the 10th annual international symposium on

Computer architecture

677:

549:

169:

139:

77:

2547:

2415:

1553:

Sharangpani, Harsh; Arora, Ken (2000). "Itanium

Processor Microarchitecture".

211:

In 2008, Itanium was the fourth-most deployed microprocessor architecture for

2848:

2338:

2328:

2287:

2024:

1112:

1042:

557:. These also have 32 static registers and 96 windowed or rotating registers.

1199:

709:

and the fastest

Itanium 2, at 1.67 GHz, was rated at 6.67 GFLOPS.

2591:

2277:

1928:

1504:"The Itanium processor, part 2: Instruction encoding, templates, and stops"

800:" to run multiple operating system instances on the processor concurrently.

734:

676:

Six multimedia units, two parallel shift units, one parallel multiply, one

462:

450:

331:

Several groups developed operating systems for the architecture, including

916:

2497:

2448:

2438:

2333:

2300:

2295:

2282:

2241:

2235:

2229:

1981:

1976:

899:

425:

419:

364:

195:

749:"Intel VT-i" redirects here. For the x86 virtualization extensions, see

534:. 32 of these are static, the other 96 are stacked using variably-sized

2736:

2731:

2586:

2525:

2470:

2443:

2387:

2268:

2223:

2217:

2192:

2186:

2180:

2159:

2153:

2087:

2072:

2012:

1555:

906:. International Symposium on Computer Architecture. New York, NY, USA:

797:

756:

Itanium processors released prior to 2006 had hardware support for the

750:

392:

360:

238:

194:

decides which instructions to execute in parallel. This contrasts with

104:

2796:

2781:

2741:

2569:

2458:

2453:

2360:

2355:

1869:

1340:

950:

690:

floating-point multiply–accumulate units (two 32-bit operations each)

655:

654:

The fetch mechanism can read up to two bundles per clock from the L1

388:

340:

317:

220:

902:(1983). "Very Long Instruction Word architectures and the ELI-512".

2791:

2370:

2019:

1881:

1671:

1575:

191:

2823:

2721:

2559:

2542:

2502:

2423:

2404:

2382:

2082:

2077:

1666:

738:

433:

380:

352:

162:

255:(RISC) architectures were approaching a processing limit at one

2746:

2512:

2365:

2350:

2059:

1891:

1401:"Intel Itanium IA-64 Support Removed With The Linux 6.7 Kernel"

786:

706:

411:

309:

216:

20:

2310:

1846:

1606:

757:

442:

348:

344:

224:

166:

39:

591:

is set to the return address when a function is called with

2658:

2475:

2345:

2323:

2119:

1226:

702:

687:

670:

Six general-purpose ALUs, two integer units, one shift unit

372:

336:

324:

architectures respectively in favor of migrating to IA-64.

1652:

Some undocumented

Itanium 2 microarchitectural information

288:

server and high-performance computing (HPC) requirements.

2252:

2204:

1991:

782:

584:

8 branch registers, for the addresses of indirect jumps.

554:

522:

The architecture implements a large number of registers:

415:

1427:"Intel Itanium Architecture Software Developer's Manual"

1283:"AMD Discloses New Technologies At Microporcessor Forum"

270:

VLIW is a computer architecture concept (like RISC and

1642:

Hewlett Packard Enterprise Integrity Servers Home Page

1311:(Press release). AMD. August 10, 2000. Archived from

1285:(Press release). AMD. October 5, 1999. Archived from

402:

Intel announced the official name of the processor,

836:"The Server Biz Enjoys the X64 Upgrade Cycle in Q1"

1275:

946:"Itanium–Is there light at the end of the tunnel?"

1571:"Intel outfits Itanium processor for faster runs"

2846:

477:and the technical press has provided overviews.

1301:

1155:

1124:

2058:

1099:

507:space is 2 bytes. The architecture implements

316:decided to abandon further development of the

186:The Itanium architecture is based on explicit

1687:

473:Intel has extensively documented the Itanium

432:eighth-generation microprocessor, code-named

406:, on October 4, 1999. Within hours, the name

1333:

1327:

1004:

1002:

172:. The basic ISA specification originated at

1478:"The Itanium processor, part 1: Warming up"

1192:"Next-generation chip passes key milestone"

251:In 1989, HP began to become concerned that

16:Microprocessor instruction set architecture

1694:

1680:

969:

606:Each 128-bit instruction word is called a

23:, AMD's 64-bit extension of the IA-32 ISA.

1133:"Core-logic efforts under way for Merced"

1040:

999:

975:

915:

862:

860:

293:explicitly parallel instruction computing

1219:

943:

744:

649:

496:, but it is still widely referred to as

428:that sank on its maiden voyage in 1912.

237:

2772:Process–architecture–optimization model

1662:IA-64 tutorial, including code examples

1568:

1398:

1252:

1105:

1072:"Microprocessors — VLIW, The Past"

1064:

1036:

1034:

939:

937:

827:

781:technology" Intel integrated into some

726:operations without disturbing the main

2855:Computer-related introductions in 2001

2847:

1419:

1043:"Intel's Merced chip may slip further"

898:

857:

833:

716:

1675:

1380:from the original on February 1, 2019

1130:

815:List of Intel Itanium microprocessors

263:(VLIW) which came out of research by

2870:Very long instruction word computing

1701:

1527:

1501:

1475:

1399:Larabel, Michael (2 November 2023).

1108:"Solaris for IA-64 coming this fall"

1031:

934:

1348:from the original on April 16, 2019

908:Association for Computing Machinery

666:The execution unit groups include:

538:, or rotating for pipelined loops.

13:

733:Main memory is accessed through a

14:

2886:

1630:

1334:Anton Shilov (January 31, 2019).

1222:"Intel names Merced chip Itanium"

1041:Shankland, Stephen (1999-07-08).

253:reduced instruction set computing

2787:Intel HD, UHD, and Iris Graphics

1454:. September 2001. Archived from

1220:Kanellos, Michael (1999-10-04).

1106:Vijayan, Jaikumar (1999-09-01).

1875:P6 variant (Enhanced Pentium M)

1594:

1583:from the original on 2020-08-01

1569:Cataldo, Anthony (2001-08-30).

1562:

1547:

1536:from the original on 2018-11-01

1521:

1510:from the original on 2018-11-01

1495:

1484:from the original on 2018-11-01

1469:

1444:

1392:

1360:

1246:

1235:from the original on 2015-12-30

1213:

1184:

1143:from the original on 2016-03-06

1131:Wolfe, Alexander (1999-09-02).

1088:from the original on 2018-06-27

1053:from the original on 2012-10-24

988:from the original on 2018-04-21

958:from the original on 2012-05-03

881:from the original on 2012-03-04

846:from the original on 2016-03-03

468:

134:); 64 1-bit predicate registers

976:Takahashi, Dean (2009-05-08).

944:De Gelas, Johan (2005-11-09).

892:

834:Morgan, Timothy (2008-05-27).

642:, which always reads as true.

490:Itanium Processor Architecture

456:

246:

242:The Intel Itanium architecture

1:

2860:Instruction set architectures

1368:"Product Change Notification"

1253:Finstad, Kraig (1999-10-04).

820:

768:In 2006, with the release of

699:multiply–accumulate operation

282:

188:instruction-level parallelism

1647:Intel Itanium Specifications

1602:"Intel product announcement"

1528:Chen, Raymond (2015-07-29).

1502:Chen, Raymond (2015-07-28).

1476:Chen, Raymond (2015-07-27).

1198:. 1999-09-17. Archived from

1169:. 1998-03-10. Archived from

1016:. 2005-12-07. Archived from

1010:"Itanium: A cautionary tale"

302:

159:instruction set architecture

7:

808:

10:

2891:

1658: (archived 2007-02-23)

748:

682:Two 82-bit floating-point

494:Intel Itanium Architecture

492:(IPA), before settling on

261:very long instruction word

233:

204:, cores execute up to six

161:(ISA) of the discontinued

155:Intel Itanium architecture

27:Intel Itanium architecture

18:

2759:

2699:

2511:

2309:

2251:

2202:

2169:

2139:

2132:

2051:

1990:

1890:

1845:

1836:

1709:

910:(ACM). pp. 140–150.

138:

120:

113:

103:

93:

83:

73:

61:

53:

45:

31:

484:. Intel later called it

379:, Hewlett-Packard, IBM,

213:enterprise-class systems

183:, was released in 2001.

130:; 32 are static, 96 use

19:Not to be confused with

1637:Intel Itanium Home Page

564:always reads +0.0, and

1870:P6 variant (Pentium M)

614:each holding a 41-bit

581:always reads 1 (true).

243:

206:instructions per cycle

2865:Intel microprocessors

1263:comp.sys.mac.advocacy

917:10.1145/800046.801649

792:Hardware support for

763:IA-32 Execution Layer

745:Architectural changes

728:arithmetic logic unit

673:Four data cache units

650:Instruction execution

610:, and contains three

532:speculative execution

410:had been coined on a

257:instruction per cycle

241:

1452:"HPWorks Newsletter"

1373:. January 30, 2019.

526:128 general integer

267:in the early 1980s.

126:128 (64 bits plus 1

1615:on November 7, 2007

717:Memory architecture

684:multiply–accumulate

424:, the "unsinkable"

28:

2669:Sandy Bridge-based

1838:Microarchitectures

1823:Microarchitectures

1667:Itanium Docs at HP

1014:Tech News on ZDNet

693:Three branch units

571:always reads +1.0.

244:

99:Condition register

26:

2842:

2841:

2755:

2754:

2128:

2127:

2047:

2046:

900:Fisher, Joseph A.

629:instruction group

517:branch prediction

333:Microsoft Windows

165:family of 64-bit

148:

147:

2882:

2875:64-bit computers

2674:Ivy Bridge-based

2265:8/16-bit databus

2137:

2136:

2056:

2055:

2052:Current products

1843:

1842:

1703:Intel processors

1696:

1689:

1682:

1673:

1672:

1624:

1623:

1621:

1620:

1611:. Archived from

1598:

1592:

1591:

1589:

1588:

1566:

1560:

1551:

1545:

1544:

1542:

1541:

1525:

1519:

1518:

1516:

1515:

1499:

1493:

1492:

1490:

1489:

1473:

1467:

1466:

1464:

1463:

1448:

1442:

1441:

1439:

1438:

1429:. Archived from

1423:

1417:

1416:

1414:

1412:

1405:www.phoronix.com

1396:

1390:

1389:

1387:

1385:

1379:

1372:

1364:

1358:

1357:

1355:

1353:

1331:

1325:

1324:

1322:

1320:

1315:on March 8, 2012

1305:

1299:

1298:

1296:

1294:

1289:on March 8, 2012

1279:

1273:

1272:

1270:

1269:

1250:

1244:

1243:

1241:

1240:

1217:

1211:

1210:

1208:

1207:

1188:

1182:

1181:

1179:

1178:

1159:

1153:

1152:

1150:

1148:

1128:

1122:

1121:

1116:. Archived from

1103:

1097:

1096:

1094:

1093:

1087:

1076:

1068:

1062:

1061:

1059:

1058:

1038:

1029:

1028:

1026:

1025:

1006:

997:

996:

994:

993:

973:

967:

966:

964:

963:

941:

932:

931:

919:

896:

890:

889:

887:

886:

864:

855:

854:

852:

851:

831:

789:microprocessors.

678:population count

641:

601:

594:

590:

580:

570:

563:

544:

536:register windows

447:64-bit computing

397:VA Linux Systems

377:Cygnus Solutions

343:systems such as

314:Silicon Graphics

132:register windows

29:

25:

2890:

2889:

2885:

2884:

2883:

2881:

2880:

2879:

2845:

2844:

2843:

2838:

2767:Tick–tock model

2751:

2695:

2684:Broadwell-based

2575:Extreme Edition

2507:

2305:

2247:

2198:

2165:

2124:

2043:

1986:

1886:

1832:

1705:

1700:

1656:Wayback Machine

1633:

1628:

1627:

1618:

1616:

1600:

1599:

1595:

1586:

1584:

1567:

1563:

1552:

1548:

1539:

1537:

1526:

1522:

1513:

1511:

1500:

1496:

1487:

1485:

1474:

1470:

1461:

1459:

1450:

1449:

1445:

1436:

1434:

1425:

1424:

1420:

1410:

1408:

1397:

1393:

1383:

1381:

1377:

1370:

1366:

1365:

1361:

1351:

1349:

1332:

1328:

1318:

1316:

1307:

1306:

1302:

1292:

1290:

1281:

1280:

1276:

1267:

1265:

1251:

1247:

1238:

1236:

1218:

1214:

1205:

1203:

1190:

1189:

1185:

1176:

1174:

1161:

1160:

1156:

1146:

1144:

1129:

1125:

1104:

1100:

1091:

1089:

1085:

1074:

1070:

1069:

1065:

1056:

1054:

1039:

1032:

1023:

1021:

1008:

1007:

1000:

991:

989:

974:

970:

961:

959:

942:

935:

928:

897:

893:

884:

882:

866:

865:

858:

849:

847:

832:

828:

823:

811:

779:hyper-threading

754:

747:

737:to an off-chip

719:

661:instruction set

652:

640:

636:

618:, plus a 5-bit

599:

592:

589:

585:

579:

575:

569:

565:

562:

558:

545:always reads 0.

543:

539:

505:logical address

475:instruction set

471:

459:

414:newsgroup as a

369:Caldera Systems

305:

285:

265:Yale University

249:

236:

190:, in which the

174:Hewlett-Packard

170:microprocessors

122:General-purpose

24:

17:

12:

11:

5:

2888:

2878:

2877:

2872:

2867:

2862:

2857:

2840:

2839:

2837:

2836:

2831:

2826:

2821:

2816:

2811:

2806:

2801:

2800:

2799:

2794:

2789:

2784:

2774:

2769:

2763:

2761:

2757:

2756:

2753:

2752:

2750:

2749:

2744:

2739:

2734:

2729:

2724:

2719:

2714:

2709:

2703:

2701:

2697:

2696:

2694:

2693:

2692:

2691:

2686:

2681:

2676:

2671:

2666:

2656:

2655:

2654:

2649:

2644:

2639:

2634:

2629:

2624:

2619:

2614:

2609:

2604:

2599:

2594:

2584:

2583:

2582:

2577:

2572:

2567:

2557:

2556:

2555:

2550:

2540:

2539:

2538:

2533:

2522:

2520:

2509:

2508:

2506:

2505:

2500:

2495:

2494:

2493:

2488:

2486:NetBurst-based

2483:

2473:

2468:

2467:

2466:

2461:

2456:

2451:

2446:

2441:

2436:

2431:

2421:

2420:

2419:

2413:

2402:

2401:

2400:

2395:

2385:

2380:

2379:

2378:

2373:

2368:

2363:

2358:

2353:

2343:

2342:

2341:

2336:

2331:

2320:

2318:

2307:

2306:

2304:

2303:

2298:

2293:

2292:32-bit databus

2290:

2285:

2280:

2275:

2274:16-bit databus

2272:

2266:

2262:

2260:

2249:

2248:

2246:

2245:

2239:

2233:

2227:

2221:

2214:

2212:

2200:

2199:

2197:

2196:

2190:

2184:

2177:

2175:

2167:

2166:

2164:

2163:

2157:

2150:

2148:

2134:

2130:

2129:

2126:

2125:

2123:

2122:

2117:

2116:

2115:

2110:

2105:

2100:

2095:

2085:

2080:

2075:

2069:

2067:

2053:

2049:

2048:

2045:

2044:

2042:

2041:

2040:

2039:

2029:

2028:

2027:

2017:

2016:

2015:

2010:

1999:

1997:

1988:

1987:

1985:

1984:

1979:

1974:

1973:

1972:

1962:

1961:

1960:

1950:

1949:

1948:

1938:

1937:

1936:

1926:

1925:

1924:

1914:

1913:

1912:

1901:

1899:

1888:

1887:

1885:

1884:

1879:

1878:

1877:

1872:

1862:

1856:

1854:

1840:

1834:

1833:

1831:

1830:

1825:

1820:

1819:

1818:

1813:

1808:

1803:

1802:

1801:

1796:

1791:

1786:

1781:

1776:

1766:

1765:

1764:

1759:

1754:

1749:

1744:

1739:

1729:

1724:

1713:

1711:

1707:

1706:

1699:

1698:

1691:

1684:

1676:

1670:

1669:

1664:

1659:

1649:

1644:

1639:

1632:

1631:External links

1629:

1626:

1625:

1593:

1561:

1546:

1520:

1494:

1468:

1443:

1418:

1391:

1359:

1326:

1300:

1274:

1245:

1212:

1183:

1154:

1123:

1120:on 2000-01-15.

1098:

1081:. 2002-04-18.

1063:

1030:

998:

968:

933:

926:

891:

856:

825:

824:

822:

819:

818:

817:

810:

807:

806:

805:

801:

794:virtualization

790:

746:

743:

718:

715:

695:

694:

691:

680:

674:

671:

651:

648:

638:

604:

603:

596:

587:

582:

577:

572:

567:

560:

550:floating-point

546:

541:

470:

467:

458:

455:

304:

301:

284:

281:

248:

245:

235:

232:

146:

145:

142:

140:Floating point

136:

135:

124:

118:

117:

111:

110:

107:

101:

100:

97:

91:

90:

87:

81:

80:

75:

71:

70:

65:

59:

58:

55:

51:

50:

47:

43:

42:

33:

15:

9:

6:

4:

3:

2:

2887:

2876:

2873:

2871:

2868:

2866:

2863:

2861:

2858:

2856:

2853:

2852:

2850:

2835:

2832:

2830:

2827:

2825:

2822:

2820:

2817:

2815:

2812:

2810:

2807:

2805:

2802:

2798:

2795:

2793:

2790:

2788:

2785:

2783:

2780:

2779:

2778:

2775:

2773:

2770:

2768:

2765:

2764:

2762:

2758:

2748:

2745:

2743:

2740:

2738:

2735:

2733:

2730:

2728:

2725:

2723:

2720:

2718:

2715:

2713:

2710:

2708:

2705:

2704:

2702:

2698:

2690:

2689:Skylake-based

2687:

2685:

2682:

2680:

2679:Haswell-based

2677:

2675:

2672:

2670:

2667:

2665:

2664:Nehalem-based

2662:

2661:

2660:

2657:

2653:

2650:

2648:

2645:

2643:

2640:

2638:

2635:

2633:

2630:

2628:

2625:

2623:

2620:

2618:

2615:

2613:

2610:

2608:

2605:

2603:

2600:

2598:

2595:

2593:

2590:

2589:

2588:

2585:

2581:

2578:

2576:

2573:

2571:

2568:

2566:

2563:

2562:

2561:

2558:

2554:

2551:

2549:

2546:

2545:

2544:

2541:

2537:

2534:

2532:

2529:

2528:

2527:

2524:

2523:

2521:

2518:

2514:

2510:

2504:

2501:

2499:

2496:

2492:

2489:

2487:

2484:

2482:

2479:

2478:

2477:

2474:

2472:

2469:

2465:

2462:

2460:

2457:

2455:

2452:

2450:

2447:

2445:

2442:

2440:

2437:

2435:

2432:

2430:

2429:Original i586

2427:

2426:

2425:

2422:

2417:

2414:

2412:

2409:

2408:

2406:

2403:

2399:

2396:

2394:

2391:

2390:

2389:

2386:

2384:

2381:

2377:

2374:

2372:

2369:

2367:

2364:

2362:

2359:

2357:

2354:

2352:

2349:

2348:

2347:

2344:

2340:

2337:

2335:

2332:

2330:

2327:

2326:

2325:

2322:

2321:

2319:

2316:

2312:

2308:

2302:

2299:

2297:

2294:

2291:

2289:

2286:

2284:

2281:

2279:

2276:

2273:

2270:

2267:

2264:

2263:

2261:

2258:

2254:

2250:

2243:

2240:

2237:

2234:

2231:

2228:

2225:

2222:

2219:

2216:

2215:

2213:

2210:

2206:

2201:

2194:

2191:

2188:

2185:

2182:

2179:

2178:

2176:

2173:

2168:

2161:

2158:

2155:

2152:

2151:

2149:

2146:

2142:

2138:

2135:

2131:

2121:

2118:

2114:

2111:

2109:

2106:

2104:

2101:

2099:

2096:

2094:

2091:

2090:

2089:

2086:

2084:

2081:

2079:

2076:

2074:

2071:

2070:

2068:

2065:

2061:

2057:

2054:

2050:

2038:

2035:

2034:

2033:

2030:

2026:

2025:Goldmont Plus

2023:

2022:

2021:

2018:

2014:

2011:

2009:

2006:

2005:

2004:

2001:

2000:

1998:

1996:

1993:

1989:

1983:

1980:

1978:

1975:

1971:

1968:

1967:

1966:

1963:

1959:

1956:

1955:

1954:

1951:

1947:

1944:

1943:

1942:

1939:

1935:

1932:

1931:

1930:

1927:

1923:

1920:

1919:

1918:

1915:

1911:

1908:

1907:

1906:

1903:

1902:

1900:

1897:

1893:

1889:

1883:

1880:

1876:

1873:

1871:

1868:

1867:

1866:

1863:

1861:

1858:

1857:

1855:

1852:

1848:

1844:

1841:

1839:

1835:

1829:

1826:

1824:

1821:

1817:

1814:

1812:

1809:

1807:

1804:

1800:

1797:

1795:

1792:

1790:

1787:

1785:

1782:

1780:

1777:

1775:

1772:

1771:

1770:

1767:

1763:

1760:

1758:

1755:

1753:

1750:

1748:

1745:

1743:

1740:

1738:

1735:

1734:

1733:

1730:

1728:

1725:

1723:

1720:

1719:

1718:

1715:

1714:

1712:

1708:

1704:

1697:

1692:

1690:

1685:

1683:

1678:

1677:

1674:

1668:

1665:

1663:

1660:

1657:

1653:

1650:

1648:

1645:

1643:

1640:

1638:

1635:

1634:

1614:

1610:

1608:

1603:

1597:

1582:

1578:

1577:

1572:

1565:

1558:

1557:

1550:

1535:

1531:

1524:

1509:

1505:

1498:

1483:

1479:

1472:

1458:on 2008-11-20

1457:

1453:

1447:

1433:on 2019-04-08

1432:

1428:

1422:

1406:

1402:

1395:

1376:

1369:

1363:

1347:

1343:

1342:

1337:

1330:

1314:

1310:

1304:

1288:

1284:

1278:

1264:

1260:

1256:

1249:

1234:

1230:

1228:

1223:

1216:

1202:on 2011-08-09

1201:

1197:

1196:CNET News.com

1193:

1187:

1173:on 2004-09-20

1172:

1168:

1167:Business Wire

1164:

1158:

1142:

1138:

1134:

1127:

1119:

1115:

1114:

1113:Computerworld

1109:

1102:

1084:

1080:

1079:NY University

1073:

1067:

1052:

1048:

1044:

1037:

1035:

1020:on 2008-02-09

1019:

1015:

1011:

1005:

1003:

987:

983:

979:

972:

957:

953:

952:

947:

940:

938:

929:

927:0-89791-101-6

923:

918:

913:

909:

905:

901:

895:

880:

877:. June 2001.

876:

874:

869:

863:

861:

845:

841:

837:

830:

826:

816:

813:

812:

802:

799:

795:

791:

788:

784:

780:

775:

774:

773:

771:

766:

764:

759:

752:

742:

740:

736:

731:

729:

725:

714:

710:

708:

704:

700:

692:

689:

685:

681:

679:

675:

672:

669:

668:

667:

664:

662:

657:

647:

643:

632:

630:

626:

621:

617:

613:

609:

597:

583:

573:

556:

551:

547:

537:

533:

529:

525:

524:

523:

520:

518:

514:

510:

506:

501:

499:

495:

491:

487:

483:

478:

476:

466:

464:

454:

452:

448:

444:

439:

437:

436:

429:

427:

423:

422:

417:

413:

409:

405:

400:

398:

394:

390:

386:

382:

378:

374:

370:

366:

362:

358:

354:

350:

346:

342:

338:

334:

329:

325:

323:

319:

315:

311:

300:

296:

294:

289:

280:

277:

273:

268:

266:

262:

258:

254:

240:

231:

228:

226:

222:

218:

214:

209:

207:

203:

202:

197:

193:

189:

184:

182:

179:

175:

171:

168:

164:

160:

156:

152:

143:

141:

137:

133:

129:

125:

123:

119:

116:

112:

108:

106:

102:

98:

96:

92:

88:

86:

82:

79:

76:

72:

69:

66:

64:

60:

56:

52:

48:

44:

41:

37:

34:

30:

22:

2133:Discontinued

1970:Cypress Cove

1929:Sandy Bridge

1617:. Retrieved

1613:the original

1605:

1596:

1585:. Retrieved

1574:

1564:

1559:. pp. 38–39.

1554:

1549:

1538:. Retrieved

1523:

1512:. Retrieved

1497:

1486:. Retrieved

1471:

1460:. Retrieved

1456:the original

1446:

1435:. Retrieved

1431:the original

1421:

1409:. Retrieved

1404:

1394:

1382:. Retrieved

1362:

1350:. Retrieved

1339:

1329:

1317:. Retrieved

1313:the original

1303:

1291:. Retrieved

1287:the original

1277:

1266:. Retrieved

1255:"Re:Itanium"

1248:

1237:. Retrieved

1225:

1215:

1204:. Retrieved

1200:the original

1195:

1186:

1175:. Retrieved

1171:the original

1166:

1157:

1147:February 27,

1145:. Retrieved

1136:

1126:

1118:the original

1111:

1101:

1090:. Retrieved

1078:

1066:

1055:. Retrieved

1046:

1022:. Retrieved

1018:the original

1013:

990:. Retrieved

981:

971:

960:. Retrieved

949:

903:

894:

883:. Retrieved

871:

848:. Retrieved

839:

829:

767:

755:

732:

720:

711:

696:

665:

653:

644:

633:

628:

624:

619:

611:

607:

605:

521:

502:

497:

493:

489:

485:

481:

479:

472:

469:Architecture

463:Linux kernel

460:

440:

435:SledgeHammer

434:

430:

420:

418:on the name

407:

403:

401:

330:

326:

306:

297:

290:

286:

276:instructions

269:

250:

229:

210:

199:

185:

180:

154:

150:

149:

1982:Golden Cove

1977:Willow Cove

1958:Cannon Lake

982:VentureBeat

686:units, two

616:instruction

513:speculation

509:predication

482:PA-WideWord

457:End of life

426:ocean liner

365:Monterey/64

247:Development

196:superscalar

2849:Categories

2777:Intel GPUs

2491:Core-based

2255:(external

2143:oriented (

2013:Silvermont

1965:Sunny Cove

1934:Ivy Bridge

1717:Processors

1619:2007-05-16

1587:2020-01-19

1556:IEEE Micro

1540:2018-10-31

1514:2018-10-31

1488:2018-10-31

1462:2008-01-24

1437:2019-04-08

1411:4 November

1407:. Phoronix

1319:August 15,

1293:August 15,

1268:2013-12-19

1239:2007-04-30

1206:2007-11-01

1177:2008-10-16

1092:2018-06-26

1057:2008-10-16

1024:2007-11-01

992:2009-05-17

962:2007-03-23

885:2007-03-23

850:2008-10-29

821:References

798:hypervisor

751:Intel VT-x

393:TurboLinux

361:Tru64 UNIX

283:Production

109:Selectable

105:Endianness

78:Load–store

54:Introduced

2829:Codenames

2742:StrongARM

2580:Dual-Core

2553:Dual-Core

2464:Dual-Core

2434:OverDrive

2383:A100/A110

2376:OverDrive

2170:pre-x86 (

2037:Gracemont

1946:Broadwell

1352:April 16,

1341:AnandTech

1259:Newsgroup

1047:CNET News

951:AnandTech

840:IT Jungle

770:Montecito

724:semaphore

528:registers

341:Unix-like

303:Marketing

221:Power ISA

215:, behind

178:codenamed

157:) is the

115:Registers

95:Branching

2834:Larrabee

2712:iAPX 432

2647:11th gen

2642:10th gen

2481:P6-based

2371:RapidCAD

2113:14th gen

2108:13th gen

2103:12th gen

2098:11th gen

2093:10th gen

2020:Goldmont

2008:Saltwell

1922:Westmere

1882:NetBurst

1828:Chipsets

1609:web site

1581:Archived

1576:EE Times

1534:Archived

1508:Archived

1482:Archived

1375:Archived

1346:Archived

1233:Archived

1229:News.com

1141:Archived

1137:EE Times

1083:Archived

1051:Archived

986:Archived

956:Archived

879:Archived

844:Archived

809:See also

620:template

192:compiler

128:trap bit

85:Encoding

32:Designer

2824:Stratix

2760:Related

2722:Itanium

2637:9th gen

2632:8th gen

2627:7th gen

2622:6th gen

2617:5th gen

2612:4th gen

2607:3rd gen

2602:2nd gen

2597:1st gen

2560:Pentium

2543:Celeron

2503:Tolapai

2424:Pentium

2407:(1998)

2405:Celeron

2296:80387DX

2288:80387SX

2083:Pentium

2078:Celeron

2032:Tremont

2003:Bonnell

1953:Skylake

1941:Haswell

1917:Nehalem

1816:Itanium

1732:Pentium

1727:Celeron

1654:at the

1261::

739:chipset

730:(ALU).

593:br.call

488:, then

421:Titanic

404:Itanium

381:Red Hat

357:Solaris

353:FreeBSD

234:History

201:Tukwila

163:Itanium

2747:XScale

2517:64-bit

2513:x86-64

2418:(2004)

2315:32-bit

2278:80C187

2271:(1980)

2244:(1982)

2238:(1982)

2232:(1982)

2226:(1979)

2220:(1978)

2209:16-bit

2203:Early

2195:(1977)

2189:(1974)

2183:(1972)

2162:(1974)

2156:(1971)

2064:64-bit

2060:x86-64

1910:Penryn

1896:64-bit

1892:x86-64

1851:32-bit

1384:May 9,

924:

804:cache.

787:x86-64

707:GFLOPS

608:bundle

515:, and

412:Usenet

408:Itanic

363:, and

310:Compaq

223:, and

217:x86-64

181:Merced

63:Design

49:64-bit

21:x86-64

2819:PIIXs

2700:Other

2498:Quark

2311:IA-32

2301:80487

2283:80287

2242:80286

2236:80188

2230:80186

2172:8-bit

2145:4-bit

1847:IA-32

1811:Quark

1710:Lists

1607:Intel

1378:(PDF)

1371:(PDF)

1086:(PDF)

1075:(PDF)

758:IA-32

703:FLOPs

656:cache

625:stops

612:slots

498:IA-64

486:IA-64

443:AMD64

349:HP-UX

345:Linux

318:Alpha

225:SPARC

167:Intel

151:IA-64

89:Fixed

40:Intel

2814:ICHs

2809:SCHs

2804:PCHs

2737:i960

2732:i860

2727:RISC

2717:EPIC

2707:CISC

2659:Xeon

2587:Core

2526:Atom

2476:Xeon

2471:Core

2388:Atom

2346:i486

2324:i386

2317:x86)

2269:8087

2257:FPUs

2224:8088

2218:8086

2193:8085

2187:8080

2181:8008

2160:4040

2154:4004

2120:Xeon

2088:Core

2073:Atom

1905:Core

1853:x86)

1806:Xeon

1769:Core

1722:Atom

1413:2023

1386:2019

1354:2019

1321:2022

1295:2022

1227:CNET

1149:2016

922:ISBN

875:Labs

785:and

688:SIMD

548:128

451:code

395:and

389:SuSE

373:CERN

339:and

337:Unix

322:MIPS

320:and

312:and

272:CISC

74:Type

68:EPIC

57:2001

46:Bits

38:and

2797:Arc

2782:GMA

2531:SoC

2449:III

2439:Pro

2398:SoC

2361:DX4

2356:DX2

2334:376

2253:x87

2205:x86

2141:BCD

1995:ULV

1992:x86

1747:III

1737:Pro

912:doi

783:x86

735:bus

600:bsp

555:NaN

416:pun

385:SGI

144:128

2851::

2792:Xe

2536:CE

2444:II

2393:CE

2366:SL

2351:SX

2339:EX

2329:SX

1865:P6

1860:P5

1794:i9

1789:i7

1784:i5

1779:i3

1742:II

1604:.

1579:.

1573:.

1532:.

1506:.

1480:.

1403:.

1344:.

1338:.

1257:.

1231:.

1224:.

1194:.

1165:.

1139:.

1135:.

1110:.

1077:.

1049:.

1045:.

1033:^

1012:.

1001:^

984:.

980:.

954:.

948:.

936:^

920:.

873:HP

870:.

859:^

842:.

838:.

637:pr

586:br

576:pr

566:fr

559:fr

540:gr

511:,

500:.

465:.

391:,

387:,

383:,

375:,

371:,

359:,

355:,

351:,

347:,

335:,

227:.

219:,

208:.

36:HP

2652:M

2592:2

2570:D

2565:4

2548:D

2519:)

2515:(

2459:M

2454:4

2416:D

2411:M

2313:(

2259:)

2211:)

2207:(

2174:)

2147:)

2066:)

2062:(

1898:)

1894:(

1849:(

1799:M

1774:2

1762:M

1757:D

1752:4

1695:e

1688:t

1681:v

1622:.

1590:.

1543:.

1517:.

1491:.

1465:.

1440:.

1415:.

1388:.

1356:.

1323:.

1297:.

1271:.

1242:.

1209:.

1180:.

1151:.

1095:.

1060:.

1027:.

995:.

965:.

930:.

914::

888:.

853:.

777:"

753:.

639:0

595:.

588:0

578:0

568:1

561:0

542:0

153:(

Text is available under the Creative Commons Attribution-ShareAlike License. Additional terms may apply.